从今天开始,我将陆续推出FPGA的图像处理算法,并且包括matlab的图像处理算法与建模。

从今天开始,我将陆续推出FPGA的图像处理算法,并且包括matlab的图像处理算法与建模。

1预加重滤波器的作用 在语音信号中,声门波激励和口鼻辐射效应共同导致语音信号的高频分量能量要比低频分量弱。预加重(Pre-emphasis)的目的就是:1 .提升高频分量,平衡语音频谱,使得高频特征更加明显,便于后续的特征提取(如MFCC)。2.消除发声过程中口唇辐射的影响。3.在一定程度上抑制工频干扰。 2 预加重滤波器的使用场景 语音识别前端处理作用:这是预加重最经典和最重要的应用。平衡频

一、入门首先要掌握**HDL(HDL=verilog+VHDL**)。 第一句话是:还没学数电的先学数电。然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。因为verilog太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。

复微杯大学生电子设计大赛,是由上海复旦微电子集团股份有限公司打造的高校品牌赛事,自2019年启动以来,已成功举办七届。第八届复微杯全面升级产学研协同机制,特邀示范性微电子学院产学融合发展联盟作为指导单位。 主办单位:上海复旦微电子集团股份有限公司 承办单位:复旦大学微电子学院 协办单位:(排名不分先后) 浙江大学集成电路学院 上海交通大学集成电路学院 东南大学集成电路学院 电子科技大学

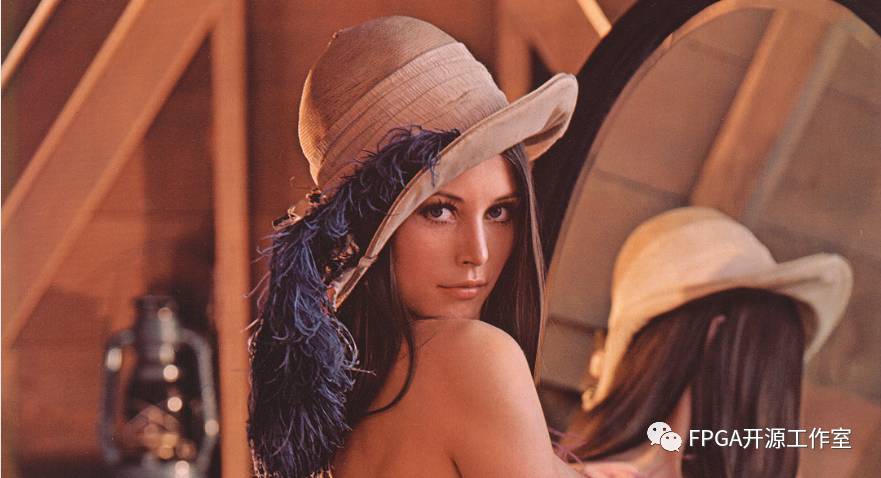

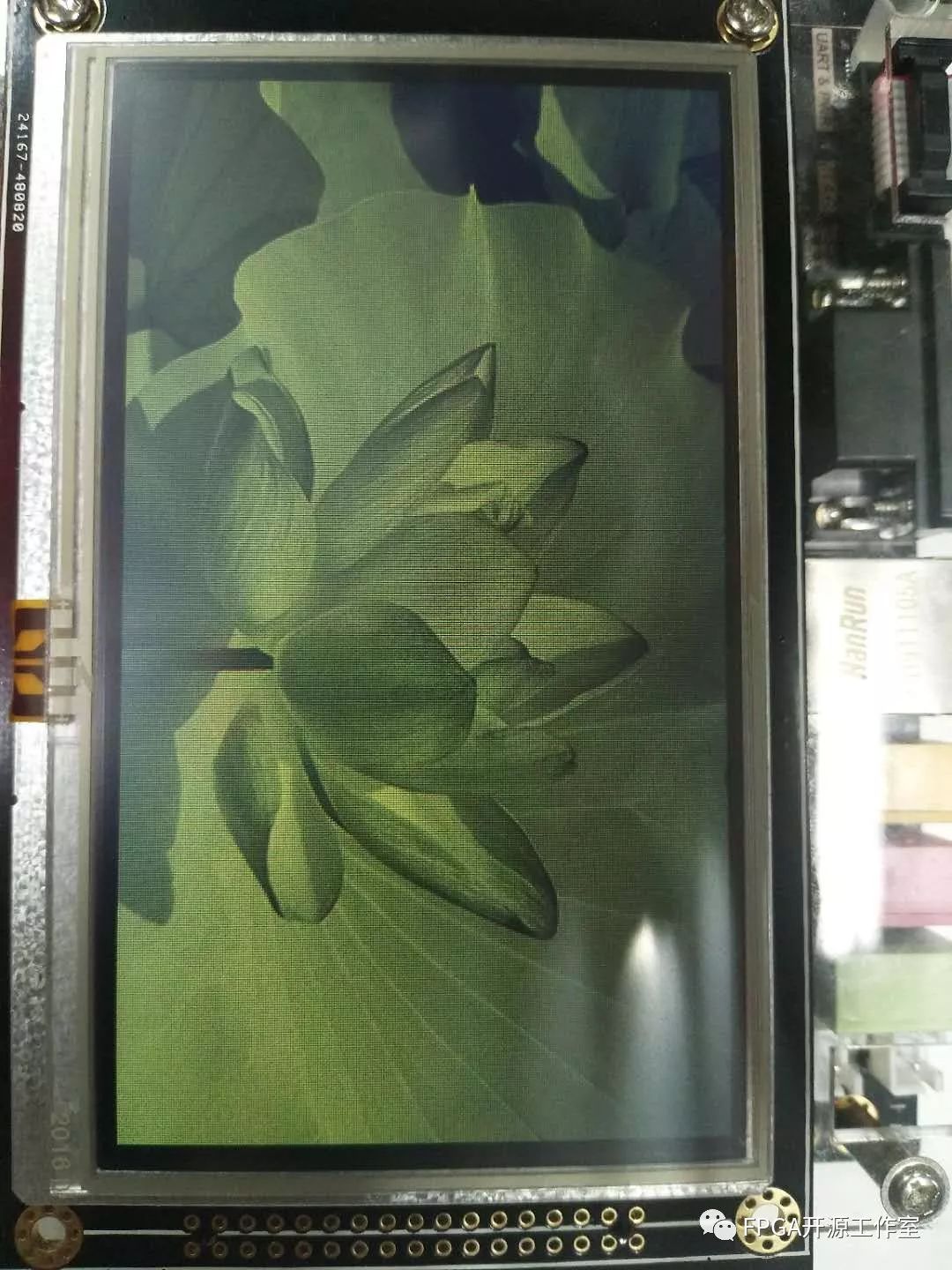

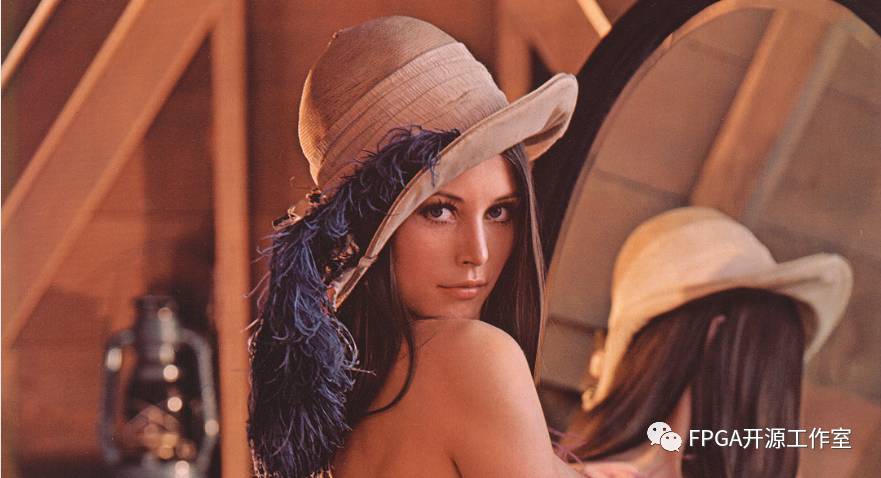

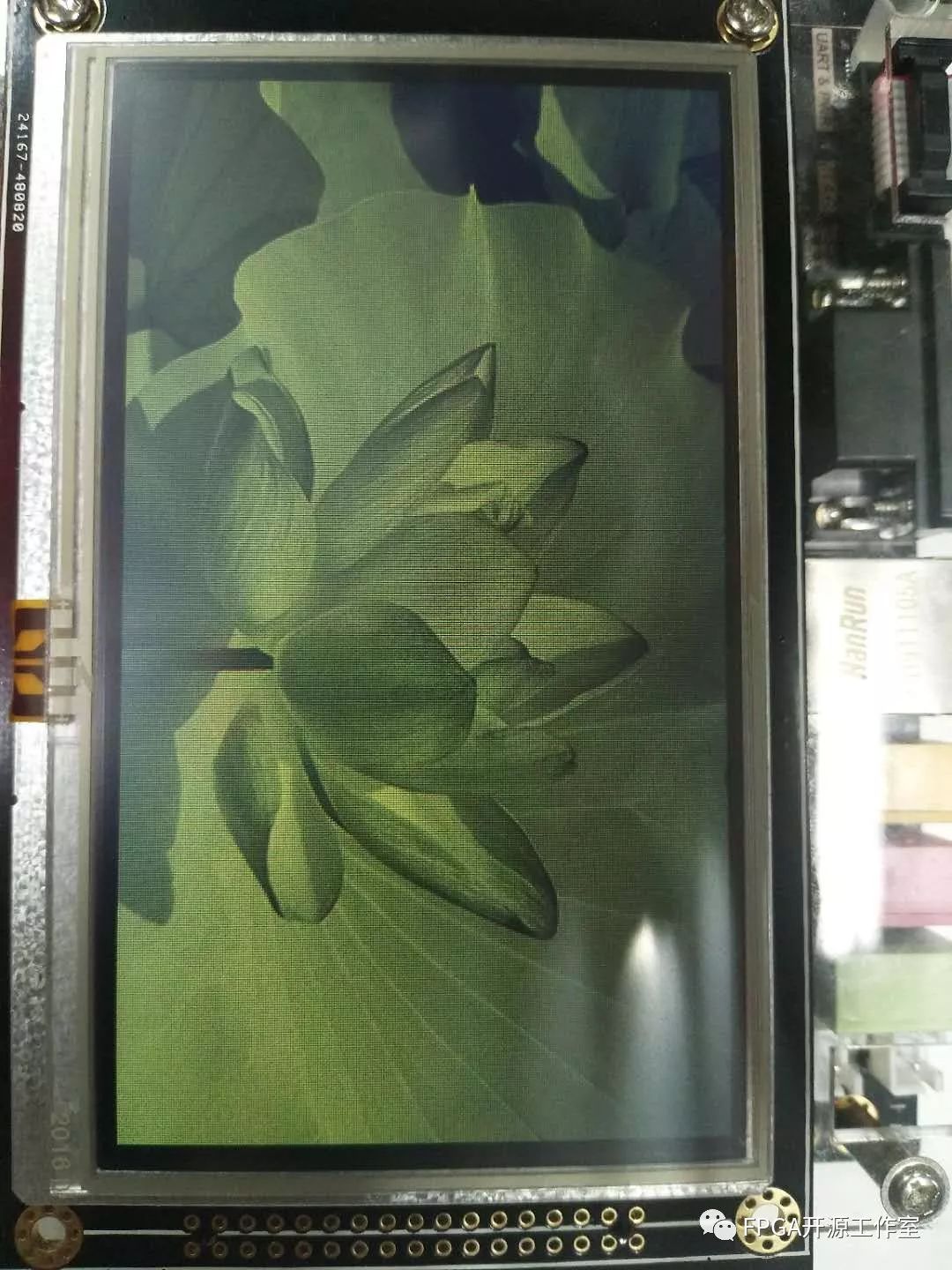

前面我们讲了基于FPGA用VGA显示一副静态图片,那么接下来我们就接着前面的工程来实现我们图像处理的基础算法里最简单的一个那就是彩色图像转灰度的实现。 将彩色图像转化为灰度的方法有两种,一个是令RGB三个分量的数值相等,输出后便可以得到灰度图像,另一种是转化为YCbCr格式,将Y分量提取出来,YCbCr格式中的Y分量表示的是图像的亮度和浓度所以只输出Y分量,得到的图像就是灰度图像了。我在这里选

什么是相控阵天线? 简单来说,相控阵天线是一种通过电子方式控制波束方向,而无需物理转动天线的先进天线系统。 它的核心组成部分是多个按一定规则排列(阵列)的独立天线单元(辐射单元),每个单元后面都连接着一个相位/幅度控制器(通常是移相器)。 1. 核心工作原理:波的干涉 相控阵天线的工作原理基于物理学中的波束形成和相干干涉。 建设性干涉:当两个或多个波的波峰与波峰相遇时,它们会相互叠加,使信号增强

将彩色图像转化为灰度的方法有两种,一个是令RGB三个分量的数值相等,输出后便可以得到灰度图像,另一种是转化为YCbCr格式,将Y分量提取出来,YCbCr格式中的Y分量表示的是图像的亮度和浓度所以只输出Y分量,得到的图像就是灰度图像了。我在这里选择第二种方法实现。 YCBCr是通过有序的三元组来表示的,三元由Y(Luminance)、Cb(Chrominance-Blue)和Cr(Chrom

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面有价值的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面是希望能帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado Schematic中的实线和虚线有什么区别? A:以下图为例:下面的schematic种,有实线也有虚线 image-20230

获奖 近日,备受行业瞩目的“2025年度华强电子网优质供应商&电子元器件行业优秀国产品牌”评选结果正式揭晓。广东高云半导体科技股份有限公司(以下简称“高云半导体”)凭借其在车规级芯片领域的技术创新与市场突破,成功斩获“2025电子元器件行业优秀汽车电子芯片国产品牌企业奖”。 此次获奖的核心产品——GW5AT-LV138UG324AA0高性能车规级FPGA,代表了国产大容量车规芯片的里程碑式

前言 在很多以太网、SATA 或其他高速接口项目中,我们经常会接触到 CRC(循环冗余校验)。通常,工程师会通过网站或软件工具生成一整套带异或操作的组合逻辑来实现 CRC 算法,而不去深入理解其原理——只知道可以这样用。事实上,在大多数情况下,确实不需要了解 CRC 的具体实现方法,这种黑盒化的使用方式在低频窄位宽场景下确实可行。 但是,当你的系统时钟非常高,例如 800MHz、1GHz,且数据位

ZYNQ算是Xilinx的一款比较高端的板子了,上面有以太网接口、USB2.0/OTG、HDMI双向接口,SD卡槽,而且板子内部还嵌入了ARM,上面可以跑linux,价格也不菲。刚开始查了一下手册了解到板子晶振是50Mhz,然后试了半天就是没有把VGA驱动起来,后来在仔细查了一下手册,这款板子在某种情况下板子提供的是125Mhz引脚为L16,然而我不知道怎么用50Mhz,那就直接

颁证仪式 近日,高云半导体基于 22nm 先进工艺平台打造的车规级 FPGA 产品——GW5AT-LV60UG225A0,成功通过国际公认的汽车电子可靠性标准 AEC-Q100 Grade 1认证。这标志着高云半导体在汽车电子领域取得了又一里程碑式的突破,为此,高云半导体与长期合作伙伴——国内领先的第三方验证分析服务机构苏试宜特共同举行了庆贺仪式暨战略合作研讨会。 苏试宜特可靠度工程部部长蔡甦谷向

为深入贯彻落实国家人工智能发展战略,系统推进公司AI战略布局,充分发挥统一战线凝聚人心、汇聚力量的强大法宝作用,近日,华大半导体召开“爱企业 献良策 做贡献”主题活动暨AI浪潮下的“芯思考”研讨会。公司党委书记、董事长孙劼出席会议并讲话,副总经理赵毅,各部门主要负责人及各所投资企业的30余名党内外专家骨干参会。 孙劼指出,人工智能是培育发展新质生产力的核心引擎,更是公司实现从“跟跑”向“并跑”

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

在工业控制和数据采集场景中,处理器与 FPGA 之间的高速数据交换是一个常见需求。传统方案通常采用 SPI(速度受限,一般 < 10Mbps)或 PCIE(带宽高但引脚多、设计复杂)。有没有一种方案,既能达到 几十 MB/s 的带宽,又只需要少量引脚,设计简单? 今天分享一个基于 睿擎派 RC3506 的方案——利用 RK3506 芯片内置的 DSMC(Double Data Rate Se

PolarFire® FPGA助力4K / 8K机器视觉快速落地 如果您正在做高速成像或机器视觉系统开发,那么好消息来了——只用一套PolarFire FPGA生态,就能同时搞定SDI、SLVS-EC 和 CoaXPress™接口! PolarFire FPGA 通过统一的平台,大幅简化设计流程,让复杂的视频接口开发变得更高效、更可控。 三种方式,全面加速您的下一代设计 SDI Rx/Tx I

文章**概述** Alchitry Au FPGA是一块专为学习、项目原型设计与高性能逻辑开发打造的 FPGA开发板。它搭载 Xilinx Artix‑7 XC7A35T‑1C 芯片,提供超过 33,000 个逻辑单元(LUT)与 256MB DDR3 RAM,在同类产品中具备非常强的处理能力与灵活性。 本文将带你全面了解这款开发板的硬件配置、外设资源、片上

在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此fpga vendor设计定制了IP核,用户通过调用IP核来实现所需功能,耗费资源少且利于时序收敛。我们在日常verilog编码过程期望通过参数化的方式调用IP核。例如IP的位宽,时延,部分关键特性期望可以通过参数调用的方式实现,而不是通过打开GUI界面通过手动选择的方式实现。其实实现方式很简单。首先通过手动打开quart

*全新的 FPGA 架构方法带来了更精细的控制和更大的灵活性,以满足机器学习 (ML) 和人工智能 (AI) 的需求。本系列文章包括两部分,*讨论了开发板与外部器件和外设(如摄像头)的连接,以及如何利用 FPGA 消除图像处理的瓶颈。 从工业控制和安全到机器人、航空航天和汽车,FPGA 在许多应用中扮演着重要角色。凭借可编程逻辑内核的灵活性及其广泛的接口能力,FPGA在可以部署机器学习 (ML)

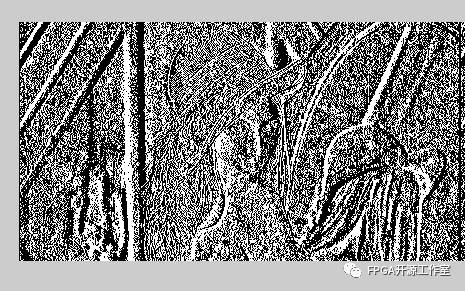

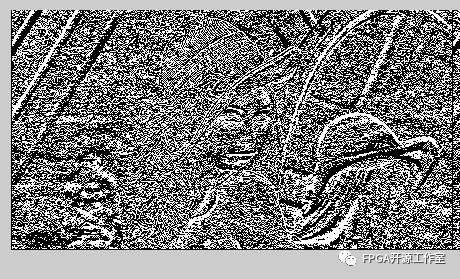

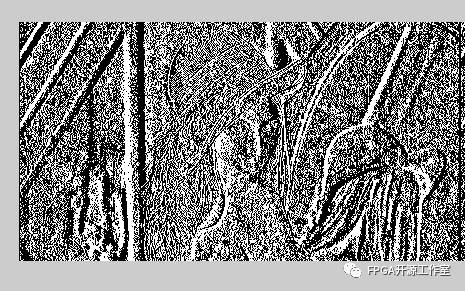

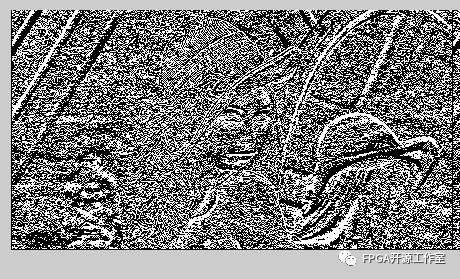

前面实现了基于FPGA的彩色图像转灰度处理,减小了图像的体积,但是其中还是存在许多噪声,会影响图像的边缘检测,所以这一篇就要消除这些噪声,基于灰度图像进行图像的滤波处理,为图像的边缘检测做好夯实基础。 椒盐噪声(salt & pepper noise)是数字图像的一个常见噪声,所谓椒盐,椒就是黑,盐就是白,椒盐噪声就是在图像上随机出现黑色白色的像素。椒盐噪声是一种因为信号脉冲强度引

前言 自从学习FPGA以来,唯一做过的完整系统就是基于basys2得多功能数字表。记得当时做的时候也没少头疼,最后用时间磨出来了一个不是很完整的小系统,当时还是产生了满满的成就感。现在回头看来,先不说功能实现的如何,首先代码书写满是不规范,其中犯得最多的一个问题就是把verilog当C来写。所以,我决定趁着寒假自由支配的时间比较多,决定重写多功能数字时钟,算是对我大二第一学期以来

评论区

登录后即可参与讨论

立即登录